ASIC pour l'électronique frontale du TileCal au HL-LHC

ASIC pour l'électronique frontale du TileCal au HL-LHC

|

Dans l'architecture actuelle du TileCal, l'électronique frontale logée dans les tiroirs est répartie dans de nombreuses cartes électroniques et à différents niveaux de l'intégration :

- Dans les blocs PMT : Le PMT, son pont diviseur passif et la carte dite 3en1 qui assume plusieurs fonctions (mise en forme du signal pulsé, intégration pour la calibration des cellules du Tilecal, sortie analogique trigger, plus injection de charges pour la calibration électronique et logique de contrôle).

- Sur une face des tiroirs : les digitiseurs qui numérisent les pulses, la carte intégrateur qui numérise les informations provenant des intégrateurs, les additionneurs qui somment les signaux trigger et l'interface qui transmet les informations numérisées vers l'extérieur via des fibres optiques.

- Sur l'autre face des tiroirs, le système de distribution et de régulation individuelle de chaque HT appliquée aux PMTs, composé de différents types de cartes.

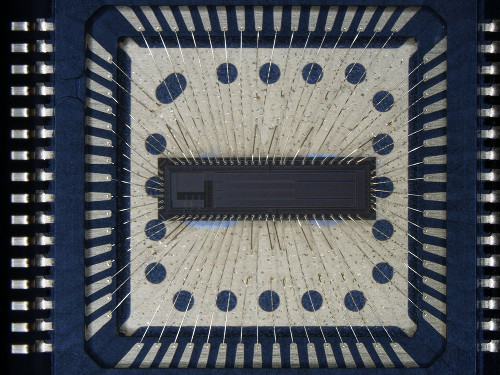

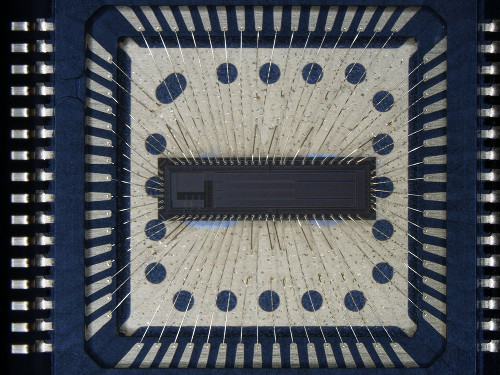

L'approche du LPC consiste à développer un composant ASIC qui contient toutes les fonctions liées à la lecture des données (signaux physiques et informations de calibration), ADC inclus : on peut parler de « Very Front End ». La nouvelle carte 3en1 accueillerait cette puce, nommée FATALIC, et quelques composants qui ne peuvent pas y figurer, tels que des régulateurs des basses tensions et autres composants (résistances et condensateurs non intégrables en raison de leurs dimensions). Seule une nouvelle carte interface subsisterait dans les tiroirs. Cette architecture correspond à l'architecture idéale recherchée.

Cette R&D menée au LPC dans la technologie GF CMOS 130 nm repose sur l'idée principale du convoyeur de courant particulièrement bien adapté aux signaux PMT et implique des études de microélectronique et un support d'électronique.

|

Malgré de très bonnes performances concernant les ADC à 40MHz, le circuit FATALIC5 (dernier né de la série), ne

permet pas de mesurer des courants sur de longues durées. Il n'a donc pas été choisi par la collaboration.

ASIC pour l'électronique frontale du TileCal au HL-LHC

ASIC pour l'électronique frontale du TileCal au HL-LHC

, directed by J. Donini, R. Madar

, directed by J. Donini, R. Madar